## Industrial CF Card

## AC46-XXXX-04X5(6) AC46-XXXX-96X5(6)

#### **Table of Contents**

| 1. Product Description                         |

|------------------------------------------------|

| 1.1 Product Overview                           |

| 1.2 Product Feature                            |

| 1.3 System Requirement                         |

| 2. Specification                               |

| 2.1 Physical Specification                     |

| 2.2 Electronic Specifications                  |

| 2.3 Performance Specifications                 |

| 2.4 Environmental Specifications               |

| 2.5 Reliability Specification                  |

| 2.6 Compliance Specifications7                 |

| 3. Function                                    |

| 3.1 Pin Signal Assignment                      |

| 3.2 CF Card Pin Signal Description             |

| 4. Access Specification 14                     |

| 4.1 Attribute Access Specifcations             |

| 4.2 Task file Register Access Specifications15 |

| 4.3 Configuration Register Specification17     |

| 4.4 CIS information                            |

| 4.5 Task file Register Specification           |

| 5. ATA Command Set 31                          |

| 6. Electrical Sepcifications                   |

| 6.1 Absolute Ratings                           |

| 6.2 Recommend Operating Conditions             |

| 6.3 DC Characteristics 1                       |

| 6.4 DC Characteristics 2                       |

| 7. AC Characteristic                              | 36   |

|---------------------------------------------------|------|

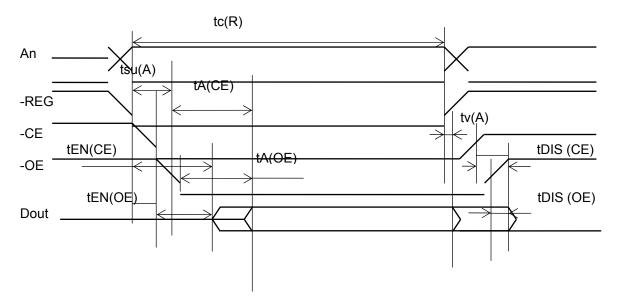

| 7.1 Attribute Memory Read AC Characteristics      | . 36 |

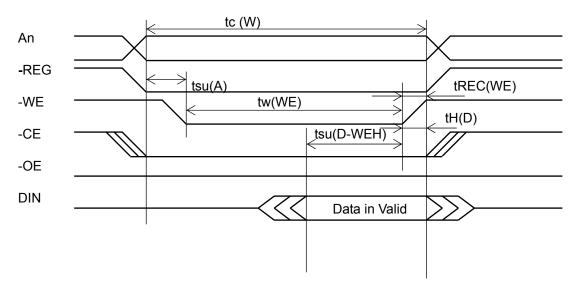

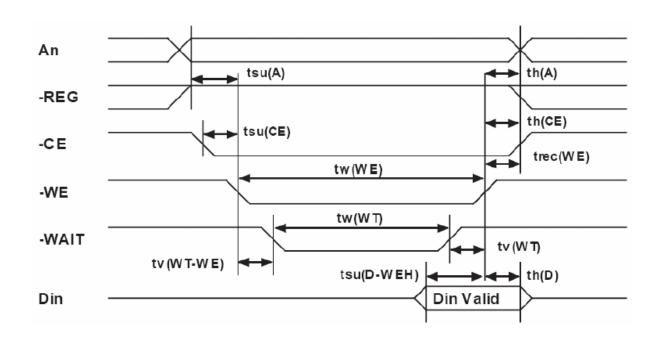

| 7.2 Attribute Memory Write Timing                 | . 37 |

| 7.3 Common Memory Read Timing Specification       | . 38 |

| 7.4 Common Memory Write Timing Specification      | . 39 |

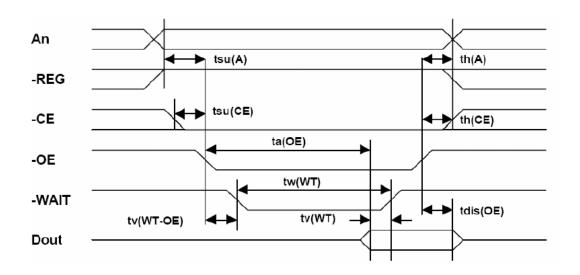

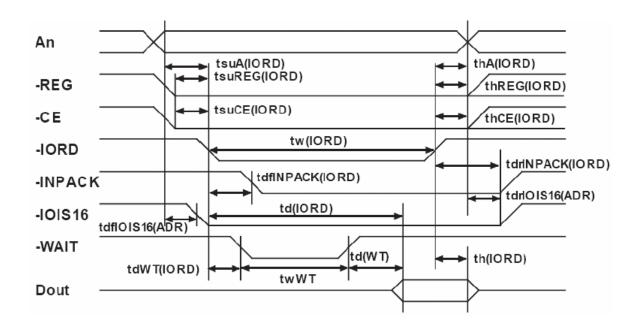

| 7.5 I/O Output (Read) Timing Specification        | . 40 |

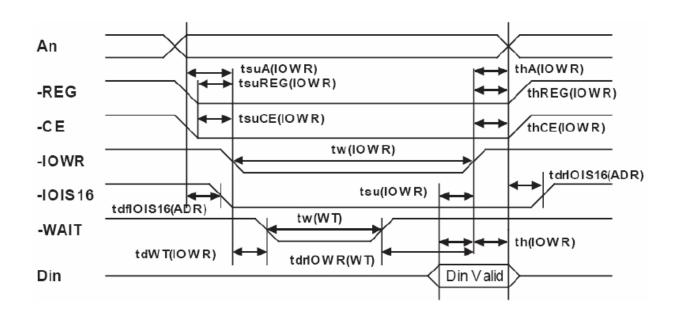

| 7.6 I/O Input (Write) Timing Specification        | . 41 |

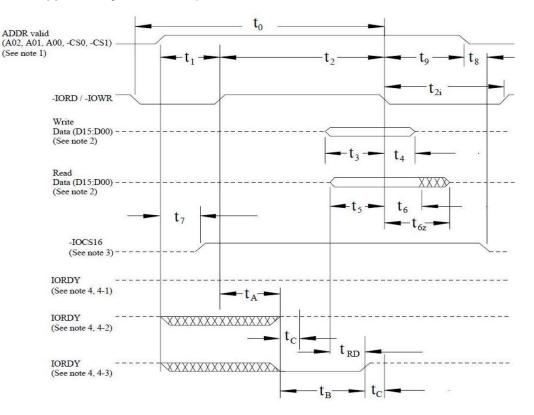

| 7.7 True IDE Mode PIO Read/Write Timing           | . 42 |

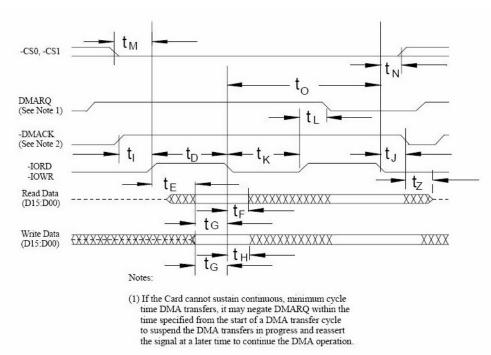

| 7.8 True IDE mode Multiword DMA Read/Write Timing | . 44 |

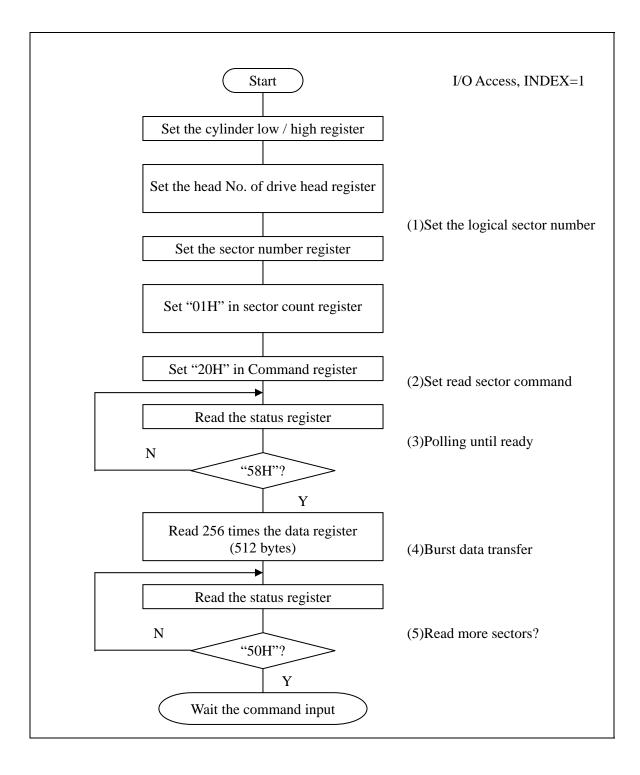

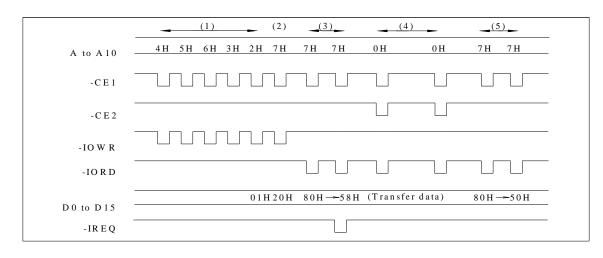

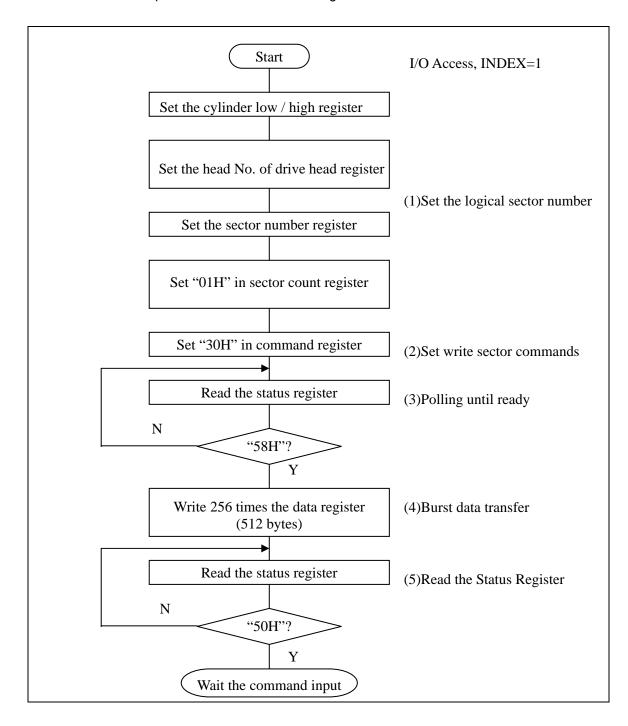

| 8. Sector Transfer Protocol                       | . 45 |

| 9. Ordering Information                           | . 49 |

| 10. Contact Information                           | . 49 |

#### List of Figures

| Figure 1: CompactFlash Storage Card Overlook Diagram | 2 |

|------------------------------------------------------|---|

| Figure 2: CompactFlash Storage Card Dimensions       | 3 |

| Figure 3: CompactFlash Storage Card Block Diagram    | 5 |

| Figure 4: CompactFlash Storage Card Signal Connector | 8 |

#### List of Tables

| Table 1: CompactFlash Storage Card Physical Dimension           | 3  |

|-----------------------------------------------------------------|----|

| Table 2 : Compact Flash Storage Card Pin Assignment             | 8  |

| Table 3 : CompactFlash Storage Card Pin Signal Description      | 9  |

| Table 4: CompactFlash Storage Card Ordering Information       4 | 19 |

#### 1. Product Description

#### 1.1 Product Overview

AC46-XXXX is **CompactFlash™** based on flash memory controller technology. This card complies with **CompactFlash™** specification; it is suitable for the usage of data storage memory for PC or other electric equipment and digital still camera. This card is equipped with NAND flash memory. By using this card it is possible to operate stability for the system that has **CompactFlash™** slots.

Fixed mode (045A)~AC46-XXXX-XXX6 disk use in system storage, some operating system can not accept boot-up from removable mode (848A)~AC46-XXXX-XXX5 disk like windows XP, when we boot-up from CFC with windows XP, the system detect the device will disable Removable device boot-up function, so the system can not finish the boot-up process. For this issue, we can set the device mode to fixed mode (045A) to solve this problem. The CFC setting to Fixed or Removable mode will no any function different or issue.

#### • Application Fields;

- Industrial PC and Thin Client

- Entertainment/Consumer Electronic Device

- Game and Telecommunication Machine

- Ticketing, Examining, testing machine

- Army, Health and Production Equipment and Machine

- Other machines and Equipments with CompactFlash<sup>™</sup> Card Interface

#### **1.2 Product Feature**

• 32MB~8GBflash memory card.

• CompactFlash™ specification: PCMCIA ver.2.1 and PC Card ATA ver.2.01 compatible 50pin SMT connector and type I (3.3mm).

- 3.3V/5V single power supply operation.

- Internal self-diagnostic program operates at VCC power on.

- 3 variations of access mode: Memory Card Mode, I/O Card Mode, True-IDE Mode

- High reliability based on internal ECC (Error Correcting Code) Function.

- Data reliability is 1 error in 10<sup>14</sup> bits read.

- Support PIO Mode4 and MDMA mode2

- Power Consumption (3.3V/5.0V)

- High Read/Write Speed

Notice : The performance will depend on different platform with different test result.

#### 1.3 System Requirement

- The Host system which is connected to Industrial CompactFlash Storage Card should meet system requirements at minimum;

1.3.1 Power Requirement

• Voltage: DC +3.3V ± 5% or DC +5.0V ± 10%

1.3.2 Operating System

- Windows 98SE/ME/2000/XP/Vista

- Linux, DOS

- WinXP Embedded/WinCE

1.3.3 Interface

• PCMCIA ver.2.1 and PC Card ATA ver.2.01 compatible 50pin SMT connector and type I (3.3mm).

## 2. Specification 2.1 Physical Specification

#### 2.1.1 Overlook

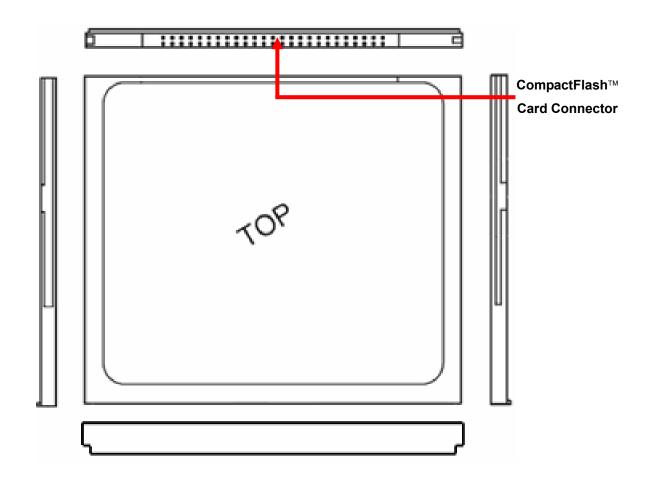

The overlook views of High Speed Industrial CompactFlash™ Storage Card are illustrated in Figure 1.

Figure 1: CompactFlash™ Storage Card Overlook Diagram

#### 2.1.2 Dimension

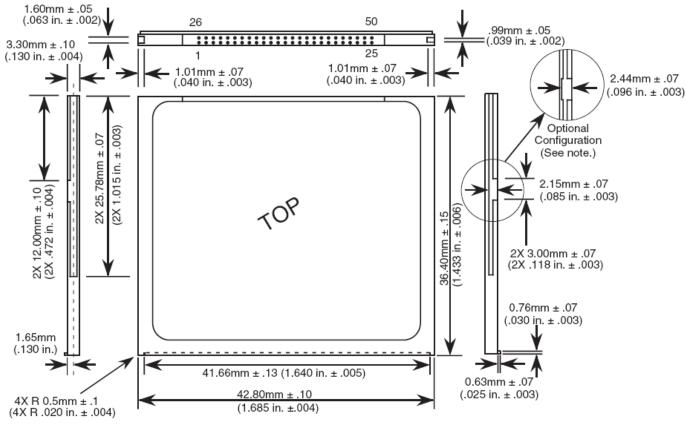

The Dimensions of CompactFlash™ Storage Card are illustrated in Figure 2 and described in Table 1.

Notice : The optional notched configuration was shown in the CFA specification Rev. 1.0 in specification Rev. 1.2, the notch was removed for ease of tooling. This optional configuration can be used but is not recommended.

Table 1: CompactFlash™ Storage Card Physical Dimension

| Length                           | 36.4 ±0.15 mm (1.433 ±0.006in.) |

|----------------------------------|---------------------------------|

| Width                            | 42.8 ±0.10 mm (1.685 ±0.004in.) |

| Thickness (Including Label Area) | 3.3 ±0.10mm (0.13 ±0.004in)     |

- 2.1.3 Weight

- Weight: 11.5g

#### 2.2 Electronic Specifications

#### 2.2.1 Product Definition

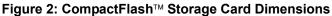

The CompacFlash<sup>™</sup> Storage Card contains a single chip controller and flash memory module(s) in a matchbook-size package with a 50-pin connector consisting of two rows of 25 female contacts each on 50 mil (1.27mm) centers. The controller interfaces with a host system allowing data to be written to and read from the flash memory modules(s).

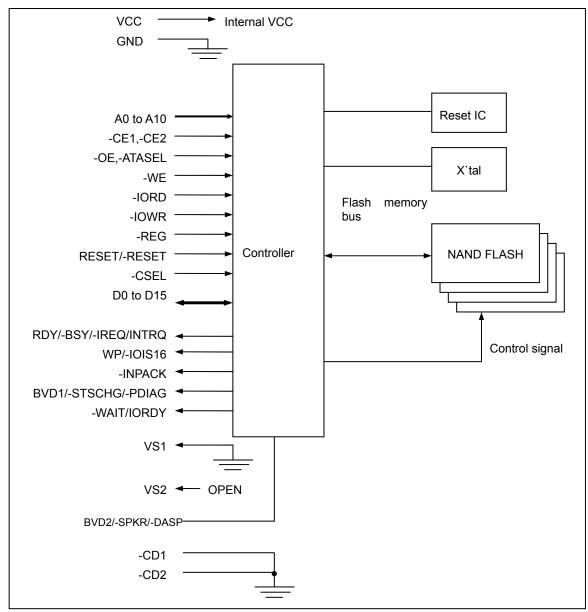

Figure 3: CompactFlash™ Storage Card Block Diagram

- 2.2.2 Operating Voltage

- Voltage DC +3.3V ± 5% or DC +5.0V ± 10%

- 2.2.3 Capacity and Block Size information

- Capacity: 32MB ~ 8GB

- Sector Size: 512Bytes

- 2.2.4 Power Consumption (3.3V/5.0V)

- Current Information

| Test Item                | 3.3V   | 5.0V   |

|--------------------------|--------|--------|

| Write Current            | 32.4mA | 36.3mA |

| Read Current             | 30.6mA | 34.1mA |

| Sleep / Stand by Current | 9.3mA  | 10.1mA |

#### 2.3 Performance Specifications

- 2.3.1 Modes

- Memory Card Mode

- I/O Card Mode

- True-IDE Mode

- PIO Mode 4 and Mulit-wordDMA mode2

2.3.2 Data Transfer Time

- Sequential Read: 8.9 MB/sec

- Sequential Write: 7.3 MB/sec

Test Platform: Average Value based on Serial ATA 1.0 Mode MB 1: Giga BX2000/Chipset: Intel 440BX+8671/CPU: P2-450MHz SDI33 256MB MB 2: MSI 6566E / Chipset: Intel 845E\_ICH4/ CPU: P4-1.8GHz DDR266 256MB Testing Software: HD Bench 3.4 & Qbench

Notice The value is various bases on the testing platform.

2.3.3 Data Retention

• 10years without requiring power support

Notice The Value of Data Retention is various bases on the type and manufacturer of Flash Memory

2.3.4 Wear-leveling

- Dynamic Wear-Leveling for same level of Write/Erase Cycle

- 2.3.5 Bad Block Management

- The Bad Blocks of Flash Memory will be replaced into new ones by controller.

#### 2.4 Environmental Specification

2.4.1 Temperature

• Industrial Type: 0°C to +70°C (Operating Temperature), -40°C to +85°C (Non Operating Temperature)

2.4.2 Humidity

- Operating Humidity (30°C Max. Wet Bulb Temp): 8% to 95%

- Non-Operating Humidity (30°C Max. Wet Bulb Temp): 8% to 95% (with no condensation relative humidity)

2.4.3 Bare Drop Testing

- Testing Conditions: 75cm height

- Testing Orientation: (Free fell) Front/Rear/Right/Left/Top/Bottom side

- Testing Result: Pass

#### 2.4.4 Vibration

Random Vibration (Operation) : Testing Specification

| Frequency (Hz) | PSD (G2/Hz) | Acceleration (Grms) | Dwell Time (Min)      |

|----------------|-------------|---------------------|-----------------------|

| 10             | 0.01        |                     | 30min per axis        |

| 100            | 0.08        | 6Grms               | $(X \cdot Y \cdot Z)$ |

| 500            | 0.08        |                     |                       |

• Random Vibration (Non-Operating): Testing Specification

| Frequency (Hz) | PSD (G2/Hz) | Acceleration (Grms) | Dwell Time (Min)              |

|----------------|-------------|---------------------|-------------------------------|

| 10             | 0.1         |                     |                               |

| 100            | 0.04        | 6Grms               | 30min per axis<br>(X • Y • Z) |

| 500            | 0.04        |                     | (*** _)                       |

| 2000           | 0.004       |                     |                               |

- Frequency Range: 3 ~ 2000Hz

- Testing Result: Pass

- 2.4.5 Shock and Altitude

- T. B. D.

#### 2.5 Reliability Specification

- 2.5.1 ECC/EDC (Error Correction Code/Error Detection Code)

- 1bytes data by 128bytes will be corrected.

- 2.5.2 Read and Write/Erase Cycle

- Read: No Limitation

- Write/Erase: 5,000,000 times

- (Estimated on reference to Doc No.SM070001)

#### 2.5.3 MTBF (Mean Time Between Failure)

- 2,000,000 hours Operating 25°C

(Estimated on reference to Dec No SM0700)

- (Estimated on reference to Doc No.SM070002)

- 2.5.4 Power Cycle

- TBD

#### 2.6 Compliance Specifications

- CE

- FCC

% Note: Please contact your closest CSS or PQI's office for other certificate information.

#### 3. Function

#### 3.1 Pin Signal Assignment

• The signals assigned for CF Card applications are described in Figure 5 and Table 2;

#### Figure 4: CompactFlash Storage Card Signal Connector

#### Table 2 : Compact Flash Storage Card Pin Assignment

|         | Memory card | mode     | I/O card m  | ode      |             | Tru      | ue IDE mode |          |

|---------|-------------|----------|-------------|----------|-------------|----------|-------------|----------|

| Pin No. |             |          |             |          | PIO mod     | le       | Multi-word  | DMA mode |

|         | Signal name | I/O      |

| 1       | GND         | _        | GND         | _        | GND         | _        | GND         | _        |

| 2       | D3          | I/O      | D3          | I/O      | D3          | I/O      | D3          | I/O      |

| 3       | D4          | I/O      | D4          | I/O      | D4          | I/O      | D4          | I/O      |

| 4       | D5          | I/O      | D5          | I/O      | D5          | I/O      | D5          | I/O      |

| 5       | D6          | I/O      | D6          | I/O      | D6          | I/O      | D6          | I/O      |

| 6       | D7          | I/O      | D7          | I/O      | D7          | I/O      | D7          | I/O      |

| 7       | -CE1        | I        | -CE1        | I        | -CS0        | I        | -CS0        | I        |

| 8       | A10         | I        | A10         | I        | A10         |          | A10         |          |

| 9       | -OE         | I        | -OE         | I        | -ATASEL     | I        | -ATASEL     | I        |

| 10      | A9          |          | A9          | I        | A9          |          | A9          | I        |

| 11      | A8          | 1        | A8          | 1        | A8          | 1        | A8          |          |

| 12      | A7          | 1        | A7          | <br>     | A7          | <br>     | A7          | I        |

| 12      |             |          |             | _        |             |          |             |          |

|         | VCC         |          | VCC         |          | VCC         | _        | VCC         |          |

| 14      | A6          | <u> </u> |

| 15      | A5          | <u> </u> |

| 16      | A4          | <u> </u> |

| 17      | A3          | <u> </u> | A3          |          | A3          |          | A3          | <u> </u> |

| 18      | A2          | <u> </u> | A2          |          | A2          |          | A2          |          |

| 19      | A1          |          | A1          |          | A1          | <u> </u> | A1          |          |

| 20      | A0          |          | A0          | <u> </u> | A0          | <u> </u> | A0          | <u> </u> |

| 21      | D0          | I/O      | D0          | I/O      | D0          | I/O      | D0          | I/O      |

| 22      | D1          | I/O      | D1          | I/O      | D1          | I/O      | D1          | I/O      |

| 23      | D2          | I/O      | D2          | I/O      | D2          | I/O      | D2          | I/O      |

| 24      | WP          | 0        | -IOIS16     | 0        | -IOIS16     | 0        | -IOIS16     | 0        |

| 25      | -CD2        | 0        | -CD2        | 0        | -CD2        | 0        | -CD2        | 0        |

| 26      | -CD1        | 0        | -CD1        | 0        | -CD1        | 0        | -CD1        | 0        |

| 27      | D11         | I/O      | D11         | I/O      | D11         | I/O      | D11         | I/O      |

| 28      | D12         | I/O      | D12         | I/O      | D12         | I/O      | D12         | I/O      |

| 29      | D13         | I/O      | D13         | I/O      | D13         | I/O      | D13         | I/O      |

| 30      | D14         | I/O      | D14         | I/O      | D14         | I/O      | D14         | I/O      |

| 31      | D15         | I/O      | D15         | I/O      | D15         | I/O      | D15         | I/O      |

| 32      | -CE2        |          | -CE2        | I        | -CS1        | I        | -CS1        | I        |

| 33      | -VS1        | 0        | -VS1        | 0        | -VS1        | 0        | -VS1        | 0        |

| 34      | -IORD       |          | -IORD       | I        | -IORD       | I        | -IORD       | I        |

| 35      | -IOWR       |          | -IOWR       | I        | -IOWR       | I        | -IOWR       |          |

| 36      | -WE         |          | -WE         |          | -WE         |          | -WE         |          |

| 37      | RDY/-BSY    | 0        | -IREQ       | 0        | INTRQ       | 0        | INTRQ       | 0        |

| 38      | VCC         |          | VCC         | _        | VCC         | _        | VCC         |          |

| 39      | -CSEL       | I        | -CSEL       | Ι        | -CSEL       | I        | -CSEL       |          |

| 40      | -VS2        | 0        | -VS2        | 0        | -VS2        | 0        | -VS2        | 0        |

| 41      | RESET       | I        | RESET       | Ι        | -RESET      | Ι        | -RESET      |          |

| 42      | -WAIT       | 0        | -WAIT       | 0        | IORDY       | 0        | IORDY       | 0        |

| 43      | -INPACK     | 0        | -INPACK     | 0        | RFU         | 0        | DMARQ       | 0        |

| 44      | -REG        | I        | -REG        | Ι        | RFU         | I        | -DMACK      | Ι        |

| 45      | BVD2        | I/O      | -SPKR       | I/O      | -DASP       | I/O      | -DASP       | I/O      |

| 46      | BVD1        | I/O      | -STSCHG     | I/O      | -PDIAG      | I/O      | -PDIAG      | I/O      |

| 47      | D8          | I/O      | D8          | I/O      | D8          | I/O      | D8          | I/O      |

| 48      | D9          | I/O      | D9          | I/O      | D9          | I/O      | D9          | I/O      |

| 49      | D10         | I/O      | D10         | I/O      | D10         | I/O      | D10         | I/O      |

| 50      | GND         | _        | GND         | _        | GND         | _        | GND         | _        |

#### 3.2 Card pin Signal Description

#### Table 3 : CompactFlash Storage Card Pin Signal Description

| Signal Name                                                           | Dir | Pin No.                         | Description                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------------------------------------------|-----|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A10 to A0<br>(PC Card Memory Mode)<br>A10 to A0<br>(PC Card I/O Mode) |     | 8,10,11,12,14,15,16,17,18,19,20 | These address lines along with the-REG signal are<br>used to select the following: The I/O port address<br>registers within the CompactFlash Storage Card or<br>CF + Card, the memory mapped port add address<br>registers within the CompactFlash Storage Card or<br>CF+ Card , a byte in the card's information structure<br>and its configuration control and status registers. |

| A2 to A0<br>(True IDE Mode)                                           |     | 18,19,20                        | In True IDE Mode only A {2:0} are used to select the one of eight registers in the Task File. The remaining address lines should be grounded by the host.                                                                                                                                                                                                                          |

| BVD1<br>(PC Card Memory Mode)                                         |     |                                 | This signal is asserted high as BVD1 is not supported                                                                                                                                                                                                                                                                                                                              |

| -STSCHG<br>(PC Card Memory Mode)                                      | I/O | 46                              | This signal is asserted low to alert the host to<br>changes in the RDY/-BSY and Write Protect states;<br>while the I/O interface is configured. Its use is<br>controlled by the Card Configured and Status<br>Register.<br>In the True IDE Mode, this input/output is the Pass                                                                                                     |

| -PDIAG<br>(True IDE Mode)                                             |     |                                 | Diagnostic signal in the Master/Slave handshake protocol.                                                                                                                                                                                                                                                                                                                          |

| BVD2<br>(PC Card Memory Mode)                                         |     |                                 | This signal is asserted high, as BVD2 is not supported.                                                                                                                                                                                                                                                                                                                            |

| -SPKR<br>(PC Card / I/O Mode)                                         | I/O | 45                              | This line is the Binary AUDIO OUTPUT FROM THE<br>CARD .if the Card does not support the Binary<br>Audio function, this line should be held negated.                                                                                                                                                                                                                                |

| -DASP<br>(True IDE Mode)                                              |     |                                 | In the True IDE Mode, this input/output is the Disk<br>Active/Slave Present signal in the Master/Slave                                                                                                                                                                                                                                                                             |

| -CD1,-CD2<br>(PC Card Memory Mode)                                    | ο   | 26,25                           | These Card Detect pins are connected to ground on<br>the CompcatFlash Storage Card or CF + Card.<br>They are used by the host to determine that the<br>CompactFlash Storage Card or CF +Card is fully<br>inserted into its socket.                                                                                                                                                 |

| -CE1,-CE2<br>(PC Card I/O Mode)                                       |     |                                 | These input signals are used both to select the card and to indicate to the card whether a byte or a word                                                                                                                                                                                                                                                                          |

| -CE1,-CE2<br>(PC Card I/O Mode)                                       | I   | 7,32                            | operation is being performed. –CE2 always<br>accesses the odd byte of the word depending on A0<br>and –CE2. A multiplexing scheme based on A1.                                                                                                                                                                                                                                     |

| -CS0,-CS1<br>(True IDE Mode)                                          |     |                                 | In the True IDE Mode CS0 is the chip select for the task file registers while CS1 is used to select the Alternate Status Register and the Device Control Register.                                                                                                                                                                                                                 |

| -CSEL<br>(PC Card Memory Mode                                         |     |                                 | This signal is not used for this mode.                                                                                                                                                                                                                                                                                                                                             |

| -CSEL<br>(PC Card I/O Mode)                                           | I   | 39                              | This internally pulled up signal is used to configure<br>this device as a Master or a Slave when configured<br>in the True IDE Mode. When this pin is grounded,                                                                                                                                                                                                                    |

| -CSEL<br>(True IDE Mode)                                              |     |                                 | this device is configured as a Master. When the pins is open, this device is configured as a Slave.                                                                                                                                                                                                                                                                                |

| Signal Name                                                                                                 | Dir | Pin No.                                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------------------------------------------------------------------|-----|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D15 to D00<br>(PC Card Memory Mode)<br>D15 to D00<br>(PC Card I/O Mode)<br>D15 to D00<br>(True IDE Mode)    | I/O | 31,30,29,28,27,49,48,47,6,5,4,3,2,23,<br>22,21 | These lines carry the Data, Commands and Status<br>information between the host and the controller.D00<br>is the LSB of the Even Byte of the Word.D08 is the<br>LSB of the Even Byte of the Word.D08 is the LSB of<br>the Odd Byte of the Word.<br>True IDE Mode, all Task File operations occur in<br>byte mode on the low order bus D00 to D07 while                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| GND<br>(PC Card Memory Mode)<br>GND<br>(PC Card I/O Mode)<br>GND<br>(True IDE Mode)                         |     | 1,50                                           | all data transfers are 16 bit using D00 to D15.<br>Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| -INPCAK<br>(PC Card Memory Mode)<br>-INPACK<br>(PC Card I/O Mode)<br>Reserved<br>(True IDE Mode<br>for PIO) |     |                                                | This signal is not used in this mode.<br>The Input Acknowledge signal is asserted by the<br>CompactFlash Storage Card or CF +Card when the<br>card is selected and responding to an I/O read<br>cycle at the address that is on the address bus. This<br>signal is used by the host to control the enable of<br>any input data buffers between the CompactFlash<br>Storage Card or CF +Card and the CPU.<br>In True IDE Mode this output signal is not used and<br>should not be connected at the host.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DMARQ<br>(True IDE Mode for<br>Multi-word DMA)                                                              | 0   | 43                                             | This signal is a DMA Request that is used for DMA data transfers between host and device. It shall be asserted by the device when it is ready to transfer data to or from the host. For Multiword DMA transfers, the direction of data transfer is controlled by –IORD and –IOWR. This signal is used in a handshake manner with –DMACK, i.e., the device shall wait until the host asserts –DMACK before negating DMARQ, and reasserting DMARQ if there is more data to transfer. DMARQ shall not be driven when the device is not selected. While a DMA operation is in progress, -CS0 and –CS1 shall be held negated and the width of the transfers shall not be 16 bits. If there is no hardware support for DMA mode in the host, this output signal is not used and should not be connected at the host. In this case, the BIOS must report that DMA mode is not supported by the host so that device drivers will not attempt DMA mode. A host that does not support DMA mode and implements both PCMCIA mode and True-IDE mode as long as this does not prevent proper operation in any mode. |

| Signal Name                      | Dir | Pin No. | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                     |

|----------------------------------|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -IORD<br>(PC Card Memory Mode)   |     |         | This signal is not used in this mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                     |

| -IORD<br>(PC Card I/O Mode)      |     | 34      | This is an I/O Read strobe generated by the host.<br>This signal gates I/O data onto the bus from the<br>CompactFlash Storage Card or CF +Card when the<br>card is configured to use the I/O interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                     |

| -IORD<br>(True IDE Mode)         |     |         | In True IDE Mode, this signal has same function as in PC Card I/O Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                     |

| -IOWR<br>(PC Card Memory Mode)   |     |         | This signal is not used in this mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                     |

| -IOWR<br>(PC Card I/O Mode)      |     | 35      | The I/O Write strobe pulse is used to clock I/O data<br>on the Card Data bus into the CompcatFlash<br>Storage Card or CF +Card controller registers when<br>the CompactFlash Storage Card or CF +Card is<br>configured to use the I/O interface. The clocking will<br>occur on the negative to positive edge of the signal<br>(Trailing edge)                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                     |

| -IOWR<br>(True IDE Mode)         |     |         | In True IDE Mode, this signal has the same function as in PC Card I/O Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                     |

| -OE<br>(PC Card Memory Mode)     |     |         | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | This is an Output Enable strobe generated by the<br>host interface. It is used to read data from the<br>CompactFlash Storage Card or CF +Card in<br>Memory Mode and to read the CIS and<br>configuration registers. |

| -OE<br>(PC Card I/O Mode)        |     | 9       | In PC Card I/O Mode. This signal is used to read the CIS and configuration registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                     |

| -ATA SEL<br>(True IDE Mode)      | -   |         | To enable True IDE Mode this input should be grounded by the host.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                     |

| RDY/BSY<br>(PC Card Memory Mode) | 0   | 37      | In Memory Mode this signal is set high when the<br>CompactFlash Storage Card or CF +Card is ready<br>to accept a new data transfer operation and held<br>low when the card is busy . The Host memory card<br>socket must provide a pull-up resistor. At power up<br>and at Reset the RDY/-BSY signal is held low<br>(busy) until the CompactFlash Storage Card or CF<br>+Card has completed its power up or reset function.<br>No access of any type should be made to the<br>CompactFlash Storage Card or CF +Card during<br>this time. The RDY/-BSY signal is held high<br>(disabled from being busy) whenever the following<br>condition is true. The CompactFlash Storage Card<br>or CF +Card has been powered up with + RESET<br>continuously disconnected or asserted. |                                                                                                                                                                                                                     |

| -IREQ<br>(PC Card I/O Mode)      |     |         | Operation-After the CompactFlash Storage Card or<br>CF + Card has been configured for I/O operation;<br>this signal is used as interrupt Request. This line is<br>strobe low to generate a pulse mode interrupt or<br>held low for a level mode interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                     |

| INTRQ<br>(True IDE Mode)         |     |         | In True IDE Mode signal is the active high interrupt Request to the host.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                     |

| Signal Name                                                                  | Dir | Pin No. | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------------------------------------------|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -REG<br>(PC Card Memory Mode)                                                |     |         | This signal is used during Memory Cycles to<br>distinguish between Common Memory and<br>Register(Attribute) Memory accesses. High for<br>Common Memory. Low for Attribute Memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| -REG<br>(PC Card I/O Mode)                                                   |     |         | The signal must also be active (low) during I/O Cycles when the I/O address is on the Bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Reserved<br>(True IDE Mode<br>for PIO)                                       |     |         | In the True IDE Mode, this input signal is not used<br>and should be driven high or connected to VCC by<br>the host.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| -DMACK<br>(True IDE Mode for<br>Multi-word DMA)                              | I   | 44      | This is a DMA acknowledge signal that is asserted<br>by the host in response to DMARQ to initiate DMA<br>transfers.<br>While DMA operations are not active, the card shall<br>ignore the –DMACK signal, including a floating<br>condition.<br>If DMA operation is not supported by a True-IDE<br>mode only host, this signal should be driven high or<br>connected to VCC by the host.<br>A host that does not support DMA mode and<br>implements both PCMCIA and True-IDE modes of<br>operation need not alter the PCMCIA mode<br>connections while in True-IDE mode as long as this<br>does not prevent proper operation all modes. |

| RESET<br>(PC Card Memory Mode)                                               |     |         | When the pin is high, this signal Resets the<br>CompactFlash Storage Card or CF +Card. The<br>CompcatFlash Storage Card or CF +Card is Reset<br>only at power up if this pin is left high or open from<br>power-up. The CompactFlash Storage Card or CF                                                                                                                                                                                                                                                                                                                                                                               |

| (PC Card I/O Mode)                                                           | I   | 41      | +Card is also Reset when the Soft Reset bit in the<br>Card Configuration Option Register is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| -RESET<br>(True IDE Mode)                                                    |     |         | In the True IDE Mode this input pin is the active low hardware reset form the host.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| VCC<br>(PC Card Memory Mode)<br>(PC Card I/O Mode)<br>(True IDE Mode)        | _   | 13,38   | +5V +3.3V power.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| -VS1 /-VS2<br>(PC Card Memory Mode)<br>(PC Card I/O Mode)<br>(True IDE Mode) | 0   | 33,40   | Voltage Sense Signals. –VS1 is grounded so that the<br>CompactFlash Storage Card or CF + Card CIS can<br>be read at 3.3 volts and –VS2 is reserved by<br>PCMCIA for a secondary voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| -WAIT<br>(PC Card Memory Mode)<br>-WAIT<br>(PC Card I/O Mode)                | 0   | 42      | The –WAIT signal is driven low by the CompactFlash<br>Storage Card or CF +Card to signal the host to delay<br>completion of a memory or I/O cycle that is in<br>progress.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| IORDY<br>(True IDE Mode)                                                     |     |         | In True IDE Mode this output signal may be used as IORDY.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Signal Name                   | Dir | Pin No. | Description                                                                                                                                                                                                                                                                                  |

|-------------------------------|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -WE<br>(PC Card Memory Mode)  |     |         | This is a signal driven by the host and used for<br>starting memory write data to the registers of the<br>CompactFlash Storage Card or CF + Card when the<br>card is configured I the memory interface mode. It is<br>also used for writing the configuration registers.                     |

| -WE<br>(PC Card I/O Mode)     | I   | 36      | In PC Card I/O Mode, this signal is used for writing the configuration registers.                                                                                                                                                                                                            |

| -WE<br>(True IDE Mode)        |     |         | In True IDE Mode this input signal is not used and should be connected to VCC by the host.                                                                                                                                                                                                   |

| WP<br>(PC Card Memory Mode)   |     |         | Memory Mode-The CompactFlash Storage Card or<br>CF + Card does not have a write protect switch. This<br>signal is held low after the completion of the reset<br>initialization sequence.                                                                                                     |

| -IOIS16<br>(PC Card I/O Mode) | 0   | 24      | I/O Operation-When the CompactFlash Storage<br>Card or CF + Card is configured for I/O Operation<br>Pin 24 is used for the –I/O Selected is 16 Bit Port<br>(-IOIS16) function. A Low signal indicates that a 16<br>bit or odd byte only operation can be performed at<br>the addressed port. |

| -IOIS16<br>(True IDE Mode)    |     |         | In True IDE Mode this output signal is asserted low when this device is expecting a word data transfer cycle.                                                                                                                                                                                |

#### 4. Access specification

#### 4.1 Attribute access specifications

When CIS-ROM region or Configuration register region is accessed, read and write operations are executed under the condition of –REG = "L" as follows. That region can be accessed by Byte/Word/Odd-byte modes, which are defined by PC card standard specifications.

#### Attribute Read Access Mode

| Mode                         | -REG | -CE2 | -CE1 | A0 | -OE | -WE | D8 to D15 | D0 to D7  |

|------------------------------|------|------|------|----|-----|-----|-----------|-----------|

| Standby mode                 | Х    | Н    | Н    | Х  | Х   | х   | High-Z    | High-Z    |

| Word access                  | L    | L    | L    | Х  | L   | Н   | invalid   | even byte |

| Note: $X \rightarrow L$ or H |      |      |      |    |     |     |           |           |

#### Attribute Write Access Mode

| Mode                         | -REG | -CE2 | -CE1 | A0 | -OE | -WE | D8 to D15  | D0 to D7   |

|------------------------------|------|------|------|----|-----|-----|------------|------------|

| Standby mode                 | ×    | Н    | Н    | ×  | ×   | ×   | Don't care | Don't care |

| Word access (16bit)          | L    | L    | L    | ×  | Н   | L   | Don't care | even byte  |

| Note: $X \rightarrow L$ or H |      |      |      |    |     |     |            |            |

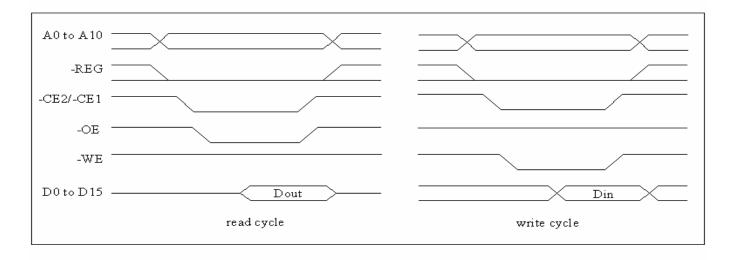

#### Attribute Access Timing Example

#### 4.2 Task file Register access specifications

There are two cases of Task File register mapping, one is mapped I/O address area, the other is mapped Memory address area. Each case of Task File registers read and write operations is executed under the condition as follows. That area can be accessed by Byte/World/Odd Byte modes, which are defined by PC card standard specifications.

#### 4.2.1 I/O address map

#### Task File Register Read Access Mode (1)

| Mode                         | -REG | -CE2 | -CE1 | A0 | -IORD | -IOWR | -OE | -WE | D8 to D15 | D0 to D7  |

|------------------------------|------|------|------|----|-------|-------|-----|-----|-----------|-----------|

| Standby mode                 | Х    | Н    | Н    | Х  | Х     | Х     | Х   | Х   | High-Z    | High-Z    |

| Word access (16bit)          | L    | L    | L    | Х  | L     | Н     | Н   | Н   | odd byte  | even byte |

| Odd byte access (8bit)       | L    | L    | Н    | Х  | L     | Н     | Н   | Н   | odd byte  | High-Z    |

| Note: $X \rightarrow L$ or H |      |      |      |    |       |       |     |     |           |           |

#### Task File Register Write Access Mode (1)

| Mode                         | -REG | -CE2 | -CE1 | A0 | -IORD | -IOWR | -OE | -WE | D8 to D15  | D0 to D7   |

|------------------------------|------|------|------|----|-------|-------|-----|-----|------------|------------|

| Standby mode                 | ×    | Н    | Н    | ×  | ×     | ×     | ×   | ×   | Don't care | Don't care |

| Word access(16-bit)          | L    | L    | L    | ×  | Н     | L     | Н   | Н   | odd byte   | even byte  |

| Note: $X \rightarrow L$ or H |      |      |      |    |       |       |     |     |            |            |

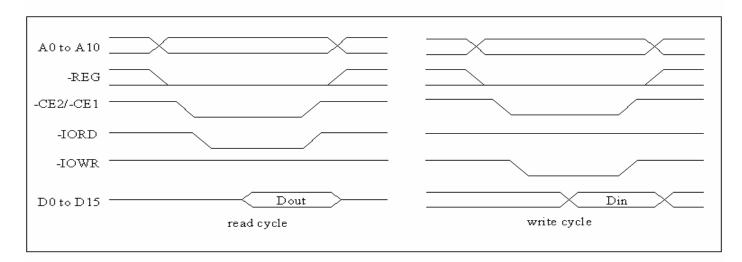

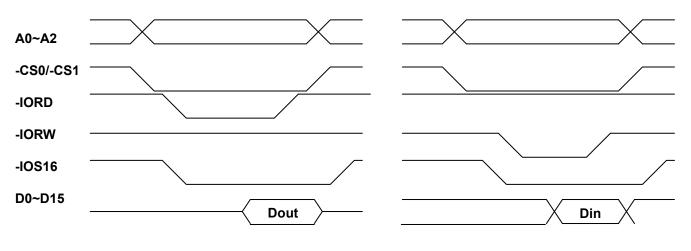

#### Task File Register Access Timing Example (1)

#### 4.2.2 Memory address map

#### Task File Register Read Access Mode (2)

| Mode                         | -REG | -CE2 | -CE1 | <b>A</b> 0 | -OE | -WE | -IORD | -IOWR | D8 to D15 | D0 to D7  |

|------------------------------|------|------|------|------------|-----|-----|-------|-------|-----------|-----------|

| Standby mode                 | Х    | Н    | Н    | Х          | Х   | Х   | Х     | Х     | High-Z    | High-Z    |

| Word access (16bit)          | Н    | L    | L    | Х          | L   | Н   | Н     | Н     | odd byte  | even byte |

| Note: $X \rightarrow L$ or H |      |      |      |            |     |     |       |       |           |           |

#### Task File Register Write Access Mode (2)

| Mode                         | -REG | -CE2 | -CE1 | A0 | -OE | -WE | -IORD | -IOWR | D8 to D15  | D0 to D7   |

|------------------------------|------|------|------|----|-----|-----|-------|-------|------------|------------|

| Standby mode                 | Х    | Н    | Н    | Х  | Х   | Х   | Х     | Х     | Don't care | Don't care |

| Word access (16bit)          | Н    | L    | L    | Х  | Н   | L   | Н     | Н     | odd byte   | even byte  |

| Note: $X \rightarrow L$ or H |      |      |      |    |     |     |       |       |            |            |

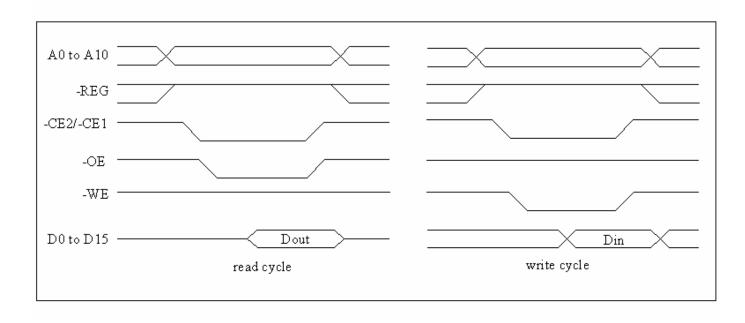

#### Task File Register Access Timing Example (2)

#### 4.2.3 True IDE Mode

The card can be configured in a True IDE This card is configured in this mode only when the –OE input signal is asserted GND by the host. In this True IDE mode Attribute Registers are not accessible from the host. Only I/O operation to the task file and data register is allowed. If this card is configured during power on sequence, data register is accessed in word (16-bit).

| Mode                         | -CS1 | -CS0 | A0~A2 | -IORD | -IOWR | D8 to D15 | D0 to D7   |

|------------------------------|------|------|-------|-------|-------|-----------|------------|

| Invalid mode                 | L    | L    | Х     | Х     | Х     | High-Z    | High-Z     |

| Standby mode                 | Н    | н    | х     | Х     | х     | High-Z    | High-Z     |

| Data register access         | Н    | L    | 0     | L     | н     | Odd byte  | even byte  |

| Alternate status access      | L    | н    | 6H    | L     | Н     | High-Z    | Status out |

| Other task file access       | Н    | L    | 1~7H  | L     | н     | High-Z    | Data       |

| Note: $X \rightarrow L$ or H |      |      |       |       |       |           |            |

#### True IDE Mode Read I/O Function

#### True IDE Mode Write I/O Function

| Mode                         | -CS1 | -CS0 | A0~A2 | -IORD | -IOWR | D8 to D15  | D0 to D7   |

|------------------------------|------|------|-------|-------|-------|------------|------------|

| Invalid mode                 | L    | L    | Х     | Х     | Х     | Don't card | Don't card |

| Standby mode                 | Н    | Н    | Х     | Х     | х     | Don't card | even byte  |

| Data register access         | Н    | L    | 0     | Н     | L     | Odd byte   | Don't card |

| Alternate status access      | L    | Н    | 6H    | Н     | L     | Don't card | Control in |

| Other task file access       | Н    | L    | 1~7H  | Н     | L     | Odd byte   | Data       |

| Note: $X \rightarrow L$ or H |      |      | •     |       | •     |            |            |

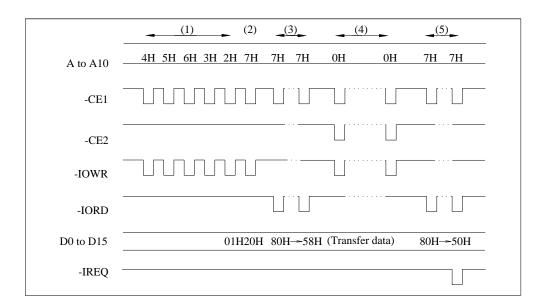

#### True IDE Mode I/O Access Timing Example

#### 4.3 Configuration register specification

This card supports four Configuration registers for the purpose of the configuration and observation of this card.

#### 4.3.1 Configuration Option register (Address 200H)

This register is used for the configuration of the card configuration status and for the issuing soft reset to the card.

| bit7                 | bit6    | bit5  | bit4 | bit3 | bit2 | bit1 | bit0 |

|----------------------|---------|-------|------|------|------|------|------|

| SRESET               | LevIREQ | INDEX |      |      |      |      |      |

| Note: initial value: | 00H     |       |      |      |      |      |      |

| Name                | R/W   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SRESET<br>(HOST->)  | R/W   | Setting this bit to "1", places the card in the reset state (Card Hard Reset). This operation is equal to Hard Reset, except this bit is not cleared. Then this bit set to "0",places the card in the reset state of Hard Reset (This bit is set to "0" by Hard Reset). Card configuration status is reset and the card internal initialized operation starts when Card Hard Reset is executed, so next access to the card should be the same sequence as the power on sequence. |

| LevIREQ<br>(HOST->) | R/W   | This bit sets to "0" when pulse mode interrupt is selected and "1 when level mode interrupt is selected.                                                                                                                                                                                                                                                                                                                                                                         |

| INDEX<br>(HOST->)   | R/W   | This bits is used for select operation mode of the card as follows.<br>When Power on, Card Hard Reset and Soft Reset, this data is "000000" for the purpose of Memory card interface recognition.                                                                                                                                                                                                                                                                                |

| Note: initial value | → 00H |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

#### INDEX bit assignment

|   | INDEX bit |   |   |   |   |             |                            |                       |  |  |  |  |  |  |

|---|-----------|---|---|---|---|-------------|----------------------------|-----------------------|--|--|--|--|--|--|

| 5 | 4         | 3 | 2 | 1 | 0 | Card mode   | Task File register address | Mapping mode          |  |  |  |  |  |  |

| 0 | 0         | 0 | 0 | 0 | 0 | Memory card | 0H to FH, 400H to 7FFH     | memory mapped         |  |  |  |  |  |  |

| 0 | 0         | 0 | 0 | 0 | 1 | I/O card    | ××0H to ××FH               | Contiguous I/O mapped |  |  |  |  |  |  |

| 0 | 0         | 0 | 0 | 1 | 0 | I/O card    | 1F0H to 1F7H, 3F6H to 3F7H | Primary I/O mapped    |  |  |  |  |  |  |

| 0 | 0         | 0 | 0 | 1 | 1 | I/O card    | 170H to 177H, 376H to 377H | Secondary I/O mapped  |  |  |  |  |  |  |

#### 4.3.2 Configuration and Status register (Address 202H) This register is used for observing the card state.

| bit7                 | bit6   | bit5  | bit4 | bit3 | bit2 | bit1 | bit0 |

|----------------------|--------|-------|------|------|------|------|------|

| CHGED                | SIGCHG | IOIS8 | 0    | 0    | PWD  | INTR | 0    |

| Nata: initial value: | 0011   |       |      |      |      | ·    |      |

Note: initial value: 00H

| Name               | R/W | Function                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHGED<br>(CARD->)  | R   | This bit indicates that CRDY-BSY bit on Pin Replacement register is set to "1". When CHGED bit is set to "1", -STSCHG pin is held "L" at the confition of SIGCHG bit set to "1" and the card configured for the I/O interface.                                                                                                                                                                                                    |

| SIGCHG<br>(HOST->) | R/W | This bit is set or reset by the host for enabling and disabling the status-change signal (-STSCHG pin). When the card is configured I/O card interface and this bit is set to "1", -STSCHG pin is controlled by CHGED bit. If this bit is set to "0", -STSCHG pin is kept "H".                                                                                                                                                    |

| IOIS8<br>(HOST->)  | R/W | The host sets this field to "1" when it can provide I/O cycles only with on 8bit data bus (D7 to D0).                                                                                                                                                                                                                                                                                                                             |

| PWD<br>(HOST->)    | R/W | When this bit is set to "1", the card enters sleep state (Power Down mode). When this bit is reset to "0", the card transfers to idle state (active mode). RRDY/-BSY bit on Pin Replacement Register becomes BUSY when this bit is changed. RRDY/-BSY will not become Ready until the power state requested has been entered. This card automatically powers down when it is idle, and powers back up when it receives a command. |

| INTR<br>(CARD->)   | R   | This bit indicates the internal state of the interrupt request. This bit state is available whether I/O card interface has been configured or not. This signal remains true until the condition which cased the interrupt request has been serviced. If interrupts are disabled by the –IEN bit in the Device Control Register, this bit is a zero.                                                                               |

#### 4.3.3 Pin Replacement register (Address 204H)

This register is used for providing the signal state of –IREQ signal when the card configured I/O card interface.

| bit7                 | bit6 | bit5      | bit4 | bit3 | bit2 | bit1      | bit0 |

|----------------------|------|-----------|------|------|------|-----------|------|

| 0                    | 0    | CRDY/-BSY | 0    | 1    | 1    | RRDY/-BSY | 0    |

| Note: initial value: | 004  |           |      |      |      |           |      |

Note: initial value: 00H

| Name                  | R/W | Function                                                                                                   |

|-----------------------|-----|------------------------------------------------------------------------------------------------------------|

| CRDY/-BSY<br>(HOST->) | R/W | This bit is set to "1" when the RRDY/-BSY bit changes state. This bit may also be written by the host.     |

| RRDY/-BSY<br>(HOST->) | R/W | When read, this bit indicates +READY pin states. When written, this bit is used for CRDY/-Bsy bit masking. |

#### 4.3.4 Socket and Copy register (Address 206H)

This register is used for identification of the card from the other card. Host can read and write this register. This register should be set by host before this card's Configuration Option register set.

| bit7                 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|----------------------|------|------|------|------|------|------|------|

| 0                    | 0    | 0    | DRV# | 0    | 0    | 0    | 0    |

| Nister Self-Lineling | 0011 |      |      |      |      |      |      |

Note: initial value: 00H

| Name             | R/W | Function                                                                                                                                                                                                                  |

|------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DRV#<br>(HOST->) | R/W | These fields are used for the configuration of the plural cards. When host configures the plural cards, written the card's copy number in this field. In this way, host can perform the card's master/slave organization. |

#### 4.4 CIS Information

CIS information of Compact Flash Card are defined as follows.

| Address | Data | 7             | 6             | 5 4     | 3           | 2         | 1       | 0  | Description of Contents                                                                   | CIS function                    |

|---------|------|---------------|---------------|---------|-------------|-----------|---------|----|-------------------------------------------------------------------------------------------|---------------------------------|

| 000H    | 01H  |               | C             | CISTPI  | _DE\        | /ICE      |         |    | Device Info tuple                                                                         | Tuple code                      |

| 002H    | 03H  |               |               | TPL     | _LIN        | <         |         |    | Link length is 3 byte                                                                     | Link to next tuple              |

| 004H    | D9H  | De            | Device Type V |         |             |           | speed   | b  | Type=D: I/O device<br>WPS=1: no WP switch<br>Speed=1: 250 ns                              | Device type, WPS, speed         |

| 006H    | 01H  | # a           | ddre          | ss unit | s –1        | ur        | nit siz | ze | 2 Kbytes of address space                                                                 | Device size                     |

| 008H    | FFH  |               |               | CIST    | PL_EN       | ١D        |         |    | End of CISTPL_DEVICE                                                                      | End marker                      |

| 00AH    | 1Ch  |               | CIS           | STPL_I  | DEVIC       | CE_C      | C       |    | Common memory other operating conditions tuple                                            | Tuple code                      |